The minimum number of J-K flip-flops required to implement this counter is Note. Design a counter that counts in the sequence 0 1 3 6.

Design Counter For Given Sequence Geeksforgeeks

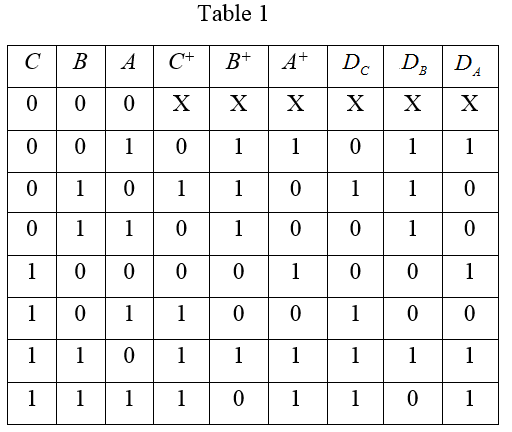

The output signals are QALSB QB AND QCMSB the input signals are DADBDCand there are active low asynchronous inputs Provide the ff Complete and labeled truth table Grouped kMAP in SOP Next state equation for all D inputs in.

. In part 1. Design a counter which counts 0 4 8 2 6 and repeats using. We want to design a synchronous counter that counts the sequence 0-1-0-2-0-3 and then repeats.

Draw the excitation table for the counter. 1 Use D Flip - flops use T flip - flops 3 Use S - R U-1- 1 use J- B U - 1 - NOW First of all we will discuss all the truth tables of flip flops. Design a synchronous counter to count the following sequence 743150743.

0 4 2 1 6. A 1 B 2 C 4 D 5 Answer. Let the type of flip-flops be RS flip-flops.

B Use J-K flip-flops. Design a mod-6 counter using JK flip-flops that sequences through the following states. Write the excitation table and circuit excitation table Table1 shows the excitation table for JK flip flop.

Implement the circuit using T-flip-flops. Arrow_forward Use d flip flop to design the sequential circuit from state diagram. Design a counter which counts in the sequence that has been assigned to you.

You dont use the 1 bit. The procedure to design a synchronous counter is as follows. Modify your design in question 1a so that the circuit works according to the following function table X Y F 0 0 Clear 0 1 No Change 1 0.

Design a decade counter which counts in the sequence. This question was asked as Numerical Answer Type. Design a counter with the following repeated binary sequence.

Simulate your design using SimUaid. A 000 001 011 101 111 010 repeat 000. Total number of states is 6.

Design A Counter That Counts In The Following Sequence. For this design 3 JK flip flops will be used. Connect the two Q terminals to outputs 1 and 2.

E Draw a complete state diagram for the counter of b showing what happens when the counter is started in each of the unused states. 0 1 3 4 5 7 0 using T flip-flop. 1c using D flip flops.

Determine the desired number of FFs From the given sequence the number of FFs is equal to 3. 0 1 2 3 4 5 6. Choose the number of flip flops using 2n N.

Design a decade counter which counts in the sequence. These values will be displayed on a seven-segment display like the one used in Lab 3. A Use D flip-flops.

1a using JK flip flops 1b using T flip flops 1c using D flip flops 2. Use JK flip flopsPlease Like Share and subscribe to my channel. Use JK flip-flops given to you at the start of the semester.

Design a counter that counts the following sequence of 2-0-1-3 and repeat. Note you may have to do a master set reset on the JK flip flops on power up so they dont enter and stay in a forbidden count sequence Ie. 0000 0100 0101 0110 0111 1000 1001 and 0001 etc.

Like this 2 - 4 - 5 - 2. Draw the logic diagram of the synchronous counter. Q1Q2Q3 001 101 110 011 010 000.

Design a counter with the following binary sequence 0 1 3 7 6 4 and represent using T flip flop. Design a counter with the following repeated binary sequence. Since it is a 3-bit counter the number of flip-flops required is three.

Design a counter that counts the following sequence of 2-3-1-0 and repeat. Also there is an enable input e which should be high for the counter to count. DATE Design a 4 bit counton which counts the Sequence ollo 1010 Doll 1111 0100 1001 01012 1110 1000 8 repeats the sequence.

Design a synchronous counter with the following sequence. Design a counter that counts the following sequence. Explanation For given.

09182736450 Design a binary counter with the sequence shown in the state diagram of Figure. The count sequence is 7-3-1-2-5-4-6. Depending on the type of clock inputs counters are of two types.

0 1 2 3 4 5 6. 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000. Design a counter to produce the following binary sequence.

This modulus six counter requires three SR flip-flops for the design. 0100 0000 0010 0110 0111 0011 0101 0001 1100 1111 1110 1010 1011 1101 1000 1001 after that it goes back to 0100 a Make the next state table for this counter b Design a digital circuit using D flip flops and minimum circuit components. The truth table of a modulus six.

D Use T flip-flops. Prerequisite Counters Problem Design synchronous counter for sequence. Design A Counter That Counts In The Following Sequence.

Choose the type of flip flop. B 000 011 101 111 010 110 repeat 000. Design a counter using d flip flops with a rising edge clock which counts in the sequence 000100111110010011 and then repeats.

Therefore the number of flip-flops required to design the counter can be. Since the sequence requires 7 states a minimum of 3 bits are required to represent all of the states. DCBA where D is the most significant bit and A the least significant bit.

Derive the flip flop input functions using K-map. C Use S-R flip-flops. The count sequence is 7-3-1-2-5-4-6.

Electrical Engineering questions and answers. The state table is as shown in Table 31. Use D flip-flops and NAND gates.

Draw the state diagram of the counter. 943 Design of a Synchronous Modulus-Six Counter Using SR Flip-Flop The modulus six counter will count 0 2 3 6 5 and 1 and repeat the sequence. Let the three flip-flops be A B and C.

The following is the count sequence.

Design Counter For Given Sequence Geeksforgeeks

Design Counter For Given Sequence Geeksforgeeks

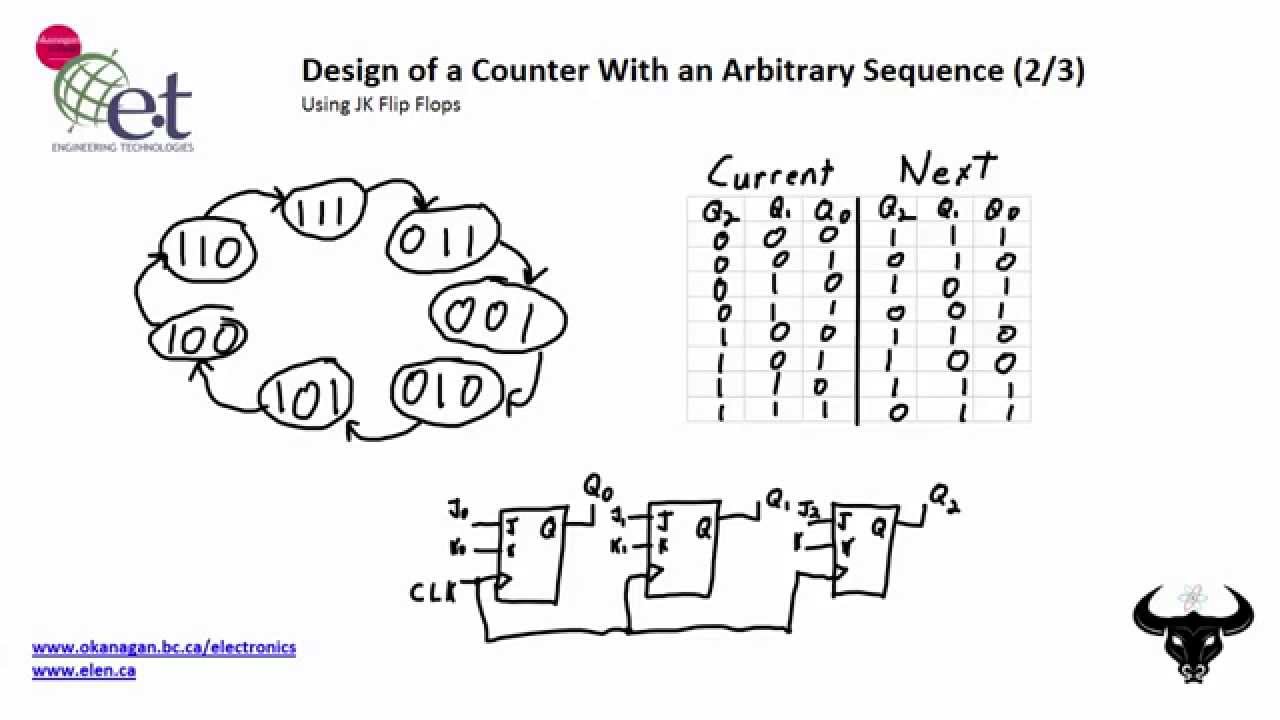

Design A Counter With An Arbitrary Sequence 2 3 Youtube

How To Design A Synchronous Counter Using D Type Flip Flops For Getting The Following Sequence 0 2 4 6 0 Quora

Solved Design A 3 Bit Counter Which Counts In The Sequence 001 Chegg Com

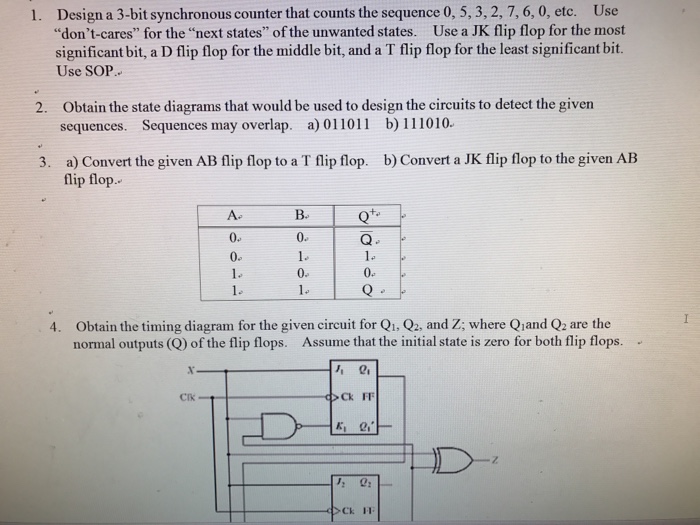

Solved Design A 3 Bit Synchronous Counter That Counts The Chegg Com

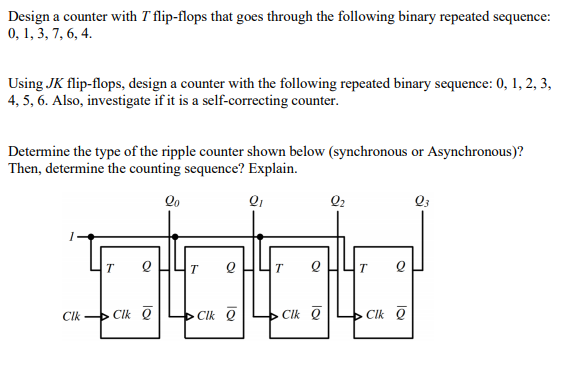

Solved Design A Counter With T Flip Flops That Goes Through Chegg Com

How To Design A Three Bit Counter That Counts In The Sequence 0 2 4 6 0 Using Jk Flip Flop Quora

0 comments

Post a Comment